Faculteit Wetenschappen Informatica

### Implementation and Evaluation of timeliness in Wireless Networks: to be or not to be - on time

Implementatie en Evaluatie van tijdigheid in Draadloze Netwerken: (op tijd) te zijn of niet te zijn

Proefschrift voorgelegd tot het behalen van de graad van Doctor in de Wetenschappen aan de Universiteit Antwerpen te verdedigen door

Wim TORFS

Promotor: Prof. Dr. Chris Blondia

Antwerpen, 2019

### Acknowledgments

I would like to thank Prof. Dr. Chris Blondia who provided me with the opportunity to obtain a PhD. In particular I would like to thank him for giving me the freedom to operate and the interesting discussions.

I would also like to thank Dr. S.A. Romaszko for sharing her expertise regarding Cognitive Radio and Rendezvous protocols. Her knowledge regarding these topics was paramount in performing the relevant research.

I would also like to thank the members of the jury for providing constructive comments and their positive encouragements.

My thanks towards the formerly PATS, and now MOSAIC, administrators, in particular Johan Bergs, who helped me numerous times with my VPN issues.

Finally, I would like to thank my wife, Sylwia, and my daughter, Izabela, for being patient and understanding of all the time spent working.

### Nederlandse samenvatting -Summary in Dutch-

Draadloze communicatie is een gebied met vele toepassingsmogelijkheden dat snel evolueert. Voor elk soort van applicatie is er wel een bepaald netwerk dat ervoor kan dienen. Binnen elk van die netwerken bevinden er zich verscheidene onderdelen waarbinnen onderzoek uitgevoerd wordt. Slechts een klein gedeelte van het beschikbare onderzoek is in dit werk beschreven, dat onderzoek uitgevoerd binnen drie verschillende netwerk types bevat, voornamelijk in de context van Medium Access Control (MAC) protocollen. De aangehaalde netwerken bevatten Wireless Sensor Networks, Wireless Local Area Networks en Cognitive Radio Networks.

Wireless Sensor Networks (WSNs) zijn bekend om hun relatief beperkte capaciteiten zowel wat betreft energie als processing power. Vandaar dat vele werken gefocust zijn op de energie efficiëntie van MAC protocollen voor wat betreft sensor netwerken. Een onderscheid kan gemaakt worden tussen een gecontroleerde medium access en een random medium access. Veel van de werken die de laatste methode gebruiken, stellen een verdeling van de beschikbare tijd voor, zodat een deel van de tijd de nodes actief zijn en een deel van de tijd energie kunnen sparen. Evenals de methode van Low Power Listening wordt gebruikt in dergelijke situaties om energie te sparen. Helaas neemt dit niet weg dat idle listening of overhearing nog steeds kunnen gebeuren. Een gecontroleerde medium access biedt de mogelijkheid om de voorgenoemde fenomenen grotendeels te elimineren dankzij de nauwkeurige controle over de transmissies en ontvangsten. Vandaar dat een groot deel van de reeds beschikbare MAC protocollen voor WSNs gebaseerd zijn op Time Division Multiple Access (TDMA). Binnen deze protocollen bestaat nog steeds een grote verscheidenheid wat betreft de methode van slot allocation. Sommige methodes gebruiken een gedistribueerde aanpak, terwijl andere dan weer een gecentraliseerde aanpak verkiezen, sommigen beschouwen zelfs een geladderde slot allocatie, etc. Wat duidelijk is, is dat er weinig werken zijn die een heterogeen network in beschouwing nemen. Met heterogeen wordt een netwerk bedoeld waarin niet elke node evenveel informatie te versturen heeft. Deze thesis neemt dergelijke netwerken wel onder beschouwing en stelt een protocol voor waarin zowel nodes met een grote hoeveelheid data, als nodes met een kleine hoeveelheid data kunnen co-existeren binnen eenzelfde netwerk. Vaak wordt de nood aan synchronisatie beschouwd als een nadeel van gecontroleerde medium access. Vandaar dat dit werk zich dan ook verdiept in bestaande synchronisatie methodes. Allereerst wordt een theoretische beschouwing gedaan van de protocollen, waarna deze wordt toegepast op hedendaagse sensor netwerk platformen. Gebaseerd op de resultaten van deze analyse is een meer efficiënt synchronisatie protocol gecontrueerd. Om de performance van dit protocol voor wat betreft efficiëntie en stabiliteit te kunnen aantonen, wordt de implementatie ervan en diens resultaten in een Proof of Concept (PoC) beschreven.

Een tweede netwerk dat beschouwd wordt in dit werk is het Wireless Local Area Network. Vanwege een hele reeks redenen zijn de specificaties opgesteld door het Institute of Electrical and Electronics Engineers (IEEE) niet geschikt voor een aantal specifieke doeleinden, zoals by. Long Range Networks, een gegarandeerde Quality of Service (QoS) voor onder andere multimedia streams of Voice over IP (VoIP) of batterijgevoede bewakingscameras. Het gebrek van bepaalde functionele elementen van de hardware, die compatibel is met de standaard, zorgt ervoor dat een minder dan optimale performance wordt bereikt in dergelijke toepassingsgebieden. Een aantal van de ondervonden problemen zijn onder andere idle listening, het gebrek van QoS garanties, de beperkte tijd voor wat betreft het ontvangen van een Acknowledgement (ACK) of het uitvoeren van een Clear Channel Assessment (CCA). Verscheidene werken hebben onderzocht hoe commercieel beschikbare hardware die voldoet aan de specificaties van de standaard kan gebruikt worden op een niet standaard manier. De onderzochte materie bij de meeste van dergelijke werken houdt in dat een gecontroleerde medium access is geplaatst bovenop de Carrier Sense Multiple Access with Collision Avoidance (CSMA/CA) medium access die door de hardware wordt aangeboden. Verscheidene manieren werden gebruikt om de doelstelling te bereiken. Een aantal werken passen de MadWiFi driver [1] aan, oftewel implementeren een laag bovenop deze driver, dewelke reeds een oudere driver is voor legacy hardware. Andere werken bereiken hun doelstelling door een combinatie van user space drivers en kernel modules die de commandos doorgeven. Nog andere werken gebruiken een ander type van hardware en passen de specifieke driver aan, of ze gebruiken de hardware in monitor mode, waardoor de gebruikelijke standaard functionaliteit van de radio wordt opgehoffen.

Ongeacht van de gebruikte methode, hebben de meeste, of zelfs alle, van deze werken hun doelstelling kunnen bereiken dankzij het open source karakter van de Linux kernel. Bij het ontwerpen of wijzigen van delen van de kernel zodat een gecontroleerde medium access mogelijk gemaakt wordt is het belangrijk om de verschillende delen van de kernel te identificeren die mogelijks een invloed kunnen hebben op de precisie waarmee de transmissie gecontroleerd wordt. Een van deze onderdelen is het process scheduling systeem dat bepaalt welke taak als volgende dient te worden uitgevoerd en bepaalt ook mede de onderlinge prioriteit van de verschillende taken. Verder is het gedeelte dat verantwoordelijk is voor het afhandelen van interrupts van belang, aangezien het het normale verloop van de processes beïnvloedt en vaak vandaar uit een tasklet of softirq gescheduled wordt, dewelke een hogere prioriteit hebben dan reguliere processen. De timer functionaliteit biedt een essentiële service van precieze timer interrupts om zodanig de transmissies en ontvangsten nauwkeurig te kunnen controleren. Uiteraard dient ook met het netwerk subsysteem van de Linux kernel rekening gehouden te worden, wat de hardware drivers implementeert, alsook de MAC functionaliteit, de Logical Link Control (LLC) en de hogere lagen met onder meer Internet Protocol (IP), User Datagram Protocol(UDP) en Transport Control Protocol(TCP). Een zekere mate van begrip omtrent deze onderdelen is vereist indien dergelijke tijds gevoelige applicaties worden ontworpen.

Aangezien de meeste hardware chips enkel maar de CSMA medium access methode ondersteunen, moet de werking van de verschillende onderdelen en functionaliteiten van de standaard, die mogelijks een invloed zouden kunnen uitoefenen op de precisie van de transmissie of ontvangst, moeten worden bestudeerd. De Distributed Coordination Function (DCF) is een van de onderdelen die hierop het meeste invloed zal hebben, maar ook met aggregation en het Block Ack mechanisme moet rekening gehouden worden, daar die toch ook een belangrijke invloedssfeer hebben. Om een dergelijke implementatie tot stand te brengen is allereerst een nauwkeurige timer source nodig. Vandaar dat een performance analyse van beschikbare timer sources is uitgevoerd foor een reeks van verschillende omgevingen en parameters. Van verscheidene Linux kernel real-time extensions en een enkel real-time operating system zijn ook mede gebruik gemaakt binnen deze analyse. Op basis van de verkregen resultaten is een van de timers geselecteerd om de precieze transmissie tijden aan te geven. De implementatie toonde nog verscheidene hardware artefacten die een invloed hadden op de nauwkeurigheid, waar voor ieder verschijnsel een oplossing of een workaround is gevonden.

Een derde netwerk dat in rekening wordt gebracht binnen dit werk is het Cognitive Radio Network (CRN). Daar waar al het voor vermelde werk gerelateerd was tot MAC protocollen, gaat dit gedeelte van het werk over een functionaliteit dit wordt uitgevoerd nog voordat de MAC laag aan het werk moet. Een CRN is een netwerk dat specifieke eigenschappen en eisen vertoont, waar aan gehouden moet worden. Bijvoorbeeld, de Primary User (PU) activiteit zou nooit onderbroken of verstoord mogen worden door een Rendezvous protocol. Verder moet er rekening gehouden worden dat een PU plots actief kan worden op het kanaal dat de Secondary Users (SUs) momenteel aan het gebruiken zijn. Vandaar dat het ontwerpen van een Rendezvous protocol de nodige aandacht vereist. Een populaire aanpak is die van channel hopping, waarbij nodes over de verschillende kanalen hoppen volgens een vastgestelde sequentie en proberen andere SUs te detecteren.

Binnen de werken die channel hopping beschouwen bestaat er nog een grote verscheidenheid over de manier waarop het hopping patroon tot stand komt. De aanpakken gaan van het aanmaken van een random hopping patroon, waarbij dan op ieder kanaal een evengrote kans is om een rendezvous te hebben, tot een voorspelbare rendezvous die gebaseerd is op numerieke analyse. Ongeacht van de varïeteit van dergelijke protocollen, de meesten nemen het natuurlijke asynchrone karakter van het systeem niet in rekening, terwijl dit net de performance enorm zou kunnen

#### beïnvloeden.

Dit werk stelt een manier voor waar op een efficiënte manier een asynchrone analyse kan uitgevoerd worden van bijna elk Rendezvous protocol. Het resultaat van die analyse toonde dat de werking op een asynchrone manier een verbetering met zich meebrengt voor wat betreft de performance van het Rendezvous protocol. Vandaar dat een extension is ontworpen die een dergelijke asynchrone werking forceert bij eender welk Rendezvous protocol door een grotere slot size te bieden aan kanalen die een hogere prioriteit hebben. Verder is in dit werk een meer geoptimaliseerde extension voorgesteld die een betere verdeling van de slot sizes over de beschikbare kanalen verzorgt. Wanneer deze extension gebruikt wordt in combinatie met een Rendezvous protocol dat specifiek was ontworpen om gebruikt te worden met deze extension, is het duidelijk dat de performance van deze combinatie ver bovenuit de performance van eender welk regulier Rendezvous protocol uitsteekt. Bemerk wel dat de meeste werken enkel maar een analyse of bewijs leveren voor een Rendezvous aan het begin van het hopping patroon. Dit werk neemt alle mogelijke rendezvous volgens dit hopping patroon in rekening en het resultaat is een statistische voorstelling van alle mogelijke rendezvous.

#### **English summary**

The area of wireless communications is a broad and fast evolving area. For each application area a specific network type is available. Those network types are composed of several subareas in which research is being performed. A small section of the available research is presented in this work, which discusses three different network types in the context of mostly Medium Access Control (MAC) protocols. The discussion includes Wireless Sensor Networks, Wireless Local Area Networks and Cognitive Radio Networks.

Wireless Sensor Networks (WSNs) are characterized by their low amount of available resources, both in terms of battery power as processing power. Most works therefore focus on the energy efficiency of MAC protocols for sensor networks. The approach taken by the different works can be divided in two main classes, a scheduled approach and an uncoordinated approach. The latter either makes use of duty cycling, or low power listening in order to reduce the energy consumption of the network. However, idle listening and overhearing is not completely eliminated by these methods. A scheduled approach can, thanks to its precise control of the transmissions and receptions, avoid most of the idle listening and overhearing. Therefore, a considerable number of MAC protocols for WSNs are Timer Division Multiple Access (TDMA) based. The slot allocation methods for those protocols come in a wide variety. Some allocation methods use distributed approaches, others a centralized approach, a staggered slot allocation might be considered, etc. However, few works actually consider a heterogeneous network in which the sensor nodes have a different amount of data to transmit. This work proposes a method which ensures that both high throughput and low throughput nodes can exist simultaneously in the same network. Note that an often considered downside of the scheduled medium access is the need for synchronization. This work elaborates on existing synchronization methods, first from a theoretical viewpoint and afterwards applied to common sensor network platforms. Based on the outcome of the analysis, a more efficient synchronization protocol is proposed, which has also been implemented in a Proof of Concept (PoC) to demonstrate its efficiency and stability.

The second type of network considered in this work is the Wireless Local Area

Network. For a wide range of reasons, the Institute of Electrical and Electronics Engineers (IEEE) specifications do not match the requirements of specific target applications, such as Long Range Networks, a guaranteed Quality of Service (QoS) for multimedia streams or Voice over IP (VoIP) or battery powered surveillance cameras. Due to the lack of certain features the default operation of the standard compliant hardware is suboptimal for such applications. The encountered issues include idle listening, the lack of a QoS guarantee, the limited timing constraints for both Acknowledgement (ACK) and Clear Channel Assessment (CCA), etc. Numerous works have been investigating the usage of Commercial Off-the-Shelf hardware (COTS) in a non-standardized manner. The modification for most of these works involves a scheduled medium access on top of the by hardware implemented Carrier Sense Multiple Access with Collision Avoidance (CSMA/CA) medium access technology. The modifications were accomplished by means of different approaches. Several works consider the modification of or implementation on top of the MadWiFi driver [1], which is a driver for older hardware. Other works consider a user space driver in combination with custom kernel modules which pass the commands. Yet other works use a different type of hardware or use it in monitoring mode, thereby disabling the usual default functionality of the radio.

Irrespective of the used methodology, most, if not all, of these works were able to complete their target thanks to the open source character of the Linux kernel. Important to consider when designing or modifying a part of the Linux kernel, in order to ensure a scheduled transmission, are the different subsystems which influence the global behavior. The process scheduling for example controls which task is to be scheduled next and determines the priority of the processes. Moreover, the interrupt handling process influences the normal operation of the process scheduling in that the Interrupt Request (IRQ) handler and the often from there scheduled tasklets and softirgs have a higher priority than a regular process. The timer subsystem provides critical functionality of accurate time interrupts in order to schedule the transmission and receptions at precise time intervals. A last subsystem which greatly influences the network operation is the network subsystem of the Linux kernel, which implements the hardware drivers, the MAC protocol, Logical Link Control (LLC), and upper layers such as Internet Protocol (IP), User Datagram Protocol(UDP) and Transport Control Protocol(TCP). A certain comprehension regarding these matters is imperative when designing such time critical application.

Considering only the CSMA access method of the standard is implemented in most hardware chips, the different functionalities which could influence the timing of the transmission or reception needs to be studied in detail. Amongst those is the Distributed Coordination Function (DCF) the one with the largest impact, notwithstanding that aggregation and the Block Ack mechanism also have a significant influence. Note that the implementation of a scheduled transmission requires a precise timer source. Therefore a performance analysis of the available timer sources is done for different environments and parameters. Several Linux kernel real-time extensions and a single real-time operating system are included in the timer source performance analysis. Based on the obtained results, one of the timers is selected as a source for triggering the exact transmission times. The implementation revealed several hardware functions which impacted the accuracy of the transmission time, for each of which a solution or workaround has been found.

The third considered network regards a Cognitive Radio Network (CRN). The previous work was oriented towards MAC protocols or related functionality. The work performed in the CRN considers Rendezvous protocols, which is an operation that should be performed in an earlier stage than the MAC protocol operation. A CRN is a type of network with its own specific properties that should be adhered to. As such, the Rendezvous protocol should not interfere with the operation of the Primary User (PU). Moreover, it should be taken into account that the PU could appear suddenly on the channel used by the Secondary User (SU). Therefore the design of a Rendezvous protocol requires the necessary attention. A popular approach for Rendezvous protocols is the channel hopping method, where nodes hop according to a certain channel sequence and sense the channel for any presence of other SUs.

Within the set of works that consider a channel hopping approach, a wide variety of methodologies exists in determining the hopping pattern. The approaches range from the generation of a random hopping pattern, thereby ensuring a statistical equal distribution of the rendezvous over the number of available channels, towards a most deterministic rendezvous based on numeric system analysis. However, most works do not consider the natural asynchronous character of the system, while this property could influence the performance in a great deal.

This work considers a method to perform an asynchronous analysis in a most efficient manner for any Rendezvous protocol. The outcome of such analysis showed that the asynchronous operation of the system improves the performance of the Rendezvous protocol. Therefore an extension was designed such that the asynchronism is induced on any regular protocol by assigning a larger slot to higher priority channels compared to lower priority channels. Based on the previously designed extension, an improved version has been designed, in order to improve the distribution between the slot sizes over the channel priorities. The performance of the combination with a Rendezvous protocol specifically designed to cooperate with the extension clearly shows a significant improvement compared to regular Rendezvous protocols. Note that while most works relate the performance of their proposed protocol to the start of the hopping pattern, this work considers an analysis of the entire set of possible rendezvous as a result of the generated hopping pattern.

### List of publications

- Wim Torfs, Peter De Cleyn, Chris Blondia, Daan Pareit, Nele Gheysens, Tom Van Leeuwen, Ingrid Moerman, Walter Van Brussel, Ines Clenjans, "QoSenabled internet-on-train network architecture: interworking by MMP-SCTP versus MIP" - in proceedings of the 7th International Conference on ITS Telecommunications, Sophia Antipolis, France, 2007.

- Wim Torfs, Peter De Cleyn, Chris Blondia, Daan Pareit, Ingrid Moerman, Piet Demeester, "SCTP as mobility protocol for enhancing Internet on the train" - in proceedings of the 8th International Conference on ITS Telecommunications, Hilton Phuket, Thailand, 2008.

- Wim Torfs, Chris Blondia, "QoS support for a MAC with a TDMA tree topology on the Magnetic Induction Radio IC" - in proceedings of the 29th Real-Time Systems Symposium (RTSS 2008), Work in Progress session, Barcelona, Spain, 2008.

- Wim Torfs, Chris Blondia, "WBAN implementation on Magnetic Induction Radio IC for medical remote monitoring" - in proceedings of the 1st International Workshop on Medical Applications Networking, Dresden, Germany, 2009.

- Wim Torfs, Chris Blondia, "Binary TDMA Schedule by Means of Egyptian Fractions for Real-time WSNs on TMotes" - in proceedings of Med-Hoc-Net 2010, Juan-les-Pins, France, 2010.

- 6. Wim Torfs, Chris Blondia, "Analysis of TDMA scheduling by means of Egyptian Fractions for real-time WSNs" - in EURASIP Journal on Wireless Communications and Networking 2011.

- Nicolas Letor, Wim Torfs, Chris Blondia, "Multimedia multicast performance analysis for 802.11n network cards" - in proceedings of Wireless Days 2012 (WD 12), 2012.

- Sylwia Romaszko, Wim Torfs, Sylwia Romaszko, Petri Mähönen, Chris Blondia, "An analysis of asynchronism of a neighborhood discovery protocol for cognitive radio networks" - in proceedings of IEEE PIMRC, London, UK, 2013.

- Sylwia Romaszko, Wim Torfs, Petri Mähönen, Chris Blondia, "Benefiting from an Induced Asynchronism in Neighborhood Discovery in opportunistic Cognitive Wireless Networks" - in proceedings of ACM MobiWac, Barcelona, Spain, 2013.

- 10. Sylwia Romaszko, Wim Torfs, Petri Mähönen, Chris Blondia, "AND: Asynchronous Neighborhood Discovery protocols for opportunistic Cognitive Wireless Networks" - in proceedings of IEEE WCNC, Turkey, 2014.

- Sylwia Romaszko, Wim Torfs, Petri Mähönen, Chris Blondia, "How to be an efficient Asynchronous Neighbourhood Discovery protocol in opportunistic Cognitive Wireless Networks" - in International Journal of Ad-hoc and Ubiquitous Computing, Vol. 20, No. 3, 2015.

- Wim Torfs, Chris Blondia, "TDMA on commercial of-the-shelf hardware: fact and fiction revealed" - in International Journal of Electronics and Communications, Vol. 69, No. 5, 2015.

## Contents

| Α  | cknov  | wledgments                                  | i     |

|----|--------|---------------------------------------------|-------|

| N  | ederl  | andse samenvatting                          | iii   |

| E  | nglisl | h summary                                   | vii   |

| Li | st of  | publications                                | xi    |

| Li | st of  | Tables                                      | xxi   |

| Li | st of  | Figures                                     | xxiii |

| Li | st of  | Acronyms                                    | xxix  |

| 1  | Intr   | oduction                                    | 1     |

|    | 1.1    | Networking stack                            | 4     |

|    | 1.2    | Uncoordinated vs coordinated channel access | 8     |

|    | 1.3    | Real-Time Systems                           | 11    |

|    | 1.4    | Outline and main research contributions     | 13    |

|    | 15     | Contributions                               | 16    |

|          | 1.6                                                                                      | Publications                                                             | 16                                                 |

|----------|------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|----------------------------------------------------|

| <b>2</b> | Res                                                                                      | earch Questions                                                          | 19                                                 |

|          | 2.1                                                                                      | Background                                                               | 20                                                 |

|          |                                                                                          | 2.1.1 Wireless Sensor Networks                                           | 20                                                 |

|          |                                                                                          | 2.1.2 Wireless Local Area Networks                                       | 20                                                 |

|          |                                                                                          | 2.1.3 Cognitive Radio Networks                                           | 21                                                 |

|          | 2.2                                                                                      | Synchronization in Wireless Networks                                     | 21                                                 |

|          |                                                                                          | 2.2.1 Wireless Sensor Networks                                           | 21                                                 |

|          |                                                                                          | 2.2.2 Wireless Local Area Networks                                       | 22                                                 |

|          | 2.3                                                                                      | Heterogeneous Wireless Networks                                          | 23                                                 |

|          | 2.4                                                                                      | Neighborhood Discovery performance                                       | 24                                                 |

|          |                                                                                          |                                                                          |                                                    |

| Ι        | W                                                                                        | reless Sensor Networks                                                   | <b>25</b>                                          |

|          |                                                                                          |                                                                          |                                                    |

| 3        | Intr                                                                                     | oduction in Wireless Sensor Networks                                     | 27                                                 |

| 3        | Intr<br>3.1                                                                              | oduction in Wireless Sensor Networks Contention based data transmissions | <b>27</b><br>30                                    |

| 3        |                                                                                          |                                                                          |                                                    |

| 3        | 3.1                                                                                      | Contention based data transmissions                                      | 30                                                 |

| 3        | 3.1                                                                                      | Contention based data transmissions                                      | 30<br>35                                           |

| 3        | 3.1                                                                                      | Contention based data transmissions                                      | 30<br>35<br>36                                     |

| 3        | 3.1                                                                                      | Contention based data transmissions                                      | 30<br>35<br>36<br>43                               |

| 3        | 3.1                                                                                      | Contention based data transmissions                                      | 30<br>35<br>36<br>43<br>50                         |

| 3        | 3.1<br>3.2                                                                               | Contention based data transmissions                                      | 30<br>35<br>36<br>43<br>50<br>52                   |

| 3        | <ul><li>3.1</li><li>3.2</li><li>3.3</li></ul>                                            | Contention based data transmissions                                      | 30<br>35<br>36<br>43<br>50<br>52<br>54             |

| 3        | <ul><li>3.1</li><li>3.2</li><li>3.3</li><li>3.4</li></ul>                                | Contention based data transmissions                                      | 30<br>35<br>36<br>43<br>50<br>52<br>54<br>57       |

| 3        | <ul> <li>3.1</li> <li>3.2</li> <li>3.3</li> <li>3.4</li> <li>3.5</li> <li>3.6</li> </ul> | Contention based data transmissions                                      | 30<br>35<br>36<br>43<br>50<br>52<br>54<br>57<br>58 |

|   | 4.2  | Principles and Concepts of Time Synchronization | 69  |

|---|------|-------------------------------------------------|-----|

|   | 4.3  | Synchronization in Distributed Systems          | 71  |

|   | 4.4  | Synchronization in WSNs                         | 74  |

|   |      | 4.4.1 Receiver-Receiver based synchronization   | 75  |

|   |      | 4.4.2 Sender-Receiver based synchronization     | 77  |

|   |      | 4.4.3 Receiver-Only based synchronization       | 78  |

|   | 4.5  | Hardware in Wireless Sensor Networks            | 81  |

|   |      | 4.5.1 Magnetic Induction Radio ASIC             | 81  |

|   |      | 4.5.2 TelosB sensor node                        | 84  |

|   |      | 4.5.3 CC2538                                    | 88  |

|   | 4.6  | Hardware related performance                    | 88  |

|   |      | 4.6.1 Receiver-to-receiver                      | 90  |

|   |      | 4.6.2 Two-way message exchange                  | 90  |

|   |      | 4.6.3 Receiver-only                             | 92  |

|   | 4.7  | Slot based synchronization                      | 92  |

|   |      | 4.7.1 Magnetic Induction Radio ASIC             | 93  |

|   |      | 4.7.2 TelosB                                    | 94  |

|   | 4.8  | Proof of Concept                                | 96  |

|   | 4.9  | Conclusion                                      | 100 |

| 5 | Fair | Scheduling MAC in Wireless Sensor Networks 1    | 03  |

| J |      |                                                 |     |

|   | 5.1  |                                                 | 103 |

|   | 5.2  |                                                 | 106 |

|   | 5.3  | Related work                                    | 111 |

|   |      | 5.3.1 Bandwidth and Rate Distribution           | 111 |

|   |      | 5.3.2 Real-Time in WSN $\ldots$ 1               | 120 |

|   | 5.4  | GCD slot allocation                             | 125 |

|   | 5.5  | Fractional series based slot allocation         | 127 |

|         | 5.6                                  | Theore                                                                                                             | etical Scheduling Analysis                                                                                                                                  | 137                                                                                                                                          |

|---------|--------------------------------------|--------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

|         |                                      | 5.6.1                                                                                                              | fewer-term slot allocations                                                                                                                                 | 137                                                                                                                                          |

|         |                                      | 5.6.2                                                                                                              | Maximum buffer size for n-term slot allocations                                                                                                             | 144                                                                                                                                          |

|         |                                      | 5.6.3                                                                                                              | Maximum latency for n-term slot allocations $\ldots \ldots \ldots$                                                                                          | 155                                                                                                                                          |

|         |                                      | 5.6.4                                                                                                              | Discussion                                                                                                                                                  | 158                                                                                                                                          |

|         | 5.7                                  | Practi                                                                                                             | cal Scheduling Analysis                                                                                                                                     | 160                                                                                                                                          |

|         |                                      | 5.7.1                                                                                                              | Buffer size                                                                                                                                                 | 161                                                                                                                                          |

|         |                                      | 5.7.2                                                                                                              | Latency                                                                                                                                                     | 169                                                                                                                                          |

|         | 5.8                                  | Netwo                                                                                                              | rked Scheduling Analysis                                                                                                                                    | 172                                                                                                                                          |

|         | 5.9                                  | Realist                                                                                                            | tic Scheduling Analysis                                                                                                                                     | 175                                                                                                                                          |

|         |                                      | 5.9.1                                                                                                              | The design                                                                                                                                                  | 177                                                                                                                                          |

|         |                                      | 5.9.2                                                                                                              | Performance evaluation                                                                                                                                      | 180                                                                                                                                          |

|         | 5 10                                 | Conclu                                                                                                             | 1sion                                                                                                                                                       | 184                                                                                                                                          |

|         | 0.10                                 |                                                                                                                    |                                                                                                                                                             |                                                                                                                                              |

|         | 5.10                                 |                                                                                                                    |                                                                                                                                                             |                                                                                                                                              |

| II      |                                      |                                                                                                                    | ss Local Area Networks                                                                                                                                      | 189                                                                                                                                          |

| II<br>6 | W                                    | 7ireles                                                                                                            | ss Local Area Networks<br>lardized operation on IEEE Std 802.11 hardware                                                                                    | 189<br>191                                                                                                                                   |

|         | W                                    | vireles                                                                                                            |                                                                                                                                                             |                                                                                                                                              |

|         | W                                    | <b>ireles</b><br>-stand<br>Introd                                                                                  | ardized operation on IEEE Std 802.11 hardware                                                                                                               | 191                                                                                                                                          |

|         | <b>W</b><br><b>Non</b><br>6.1        | <b>ireles</b><br>-stand<br>Introd                                                                                  | lardized operation on IEEE Std 802.11 hardware                                                                                                              | <b>191</b><br>191                                                                                                                            |

|         | <b>W</b><br><b>Non</b><br>6.1        | <sup>7</sup> ireles<br>stand<br>Introd<br>IEEE                                                                     | lardized operation on IEEE Std 802.11 hardware         uction                                                                                               | <b>191</b><br>191<br>193                                                                                                                     |

|         | <b>W</b><br><b>Non</b><br>6.1        | vireles<br>-stand<br>Introd<br>IEEE<br>6.2.1                                                                       | lardized operation on IEEE Std 802.11 hardware         uction                                                                                               | <b>191</b><br>191<br>193<br>194                                                                                                              |

|         | <b>W</b><br><b>Non</b><br>6.1        | vireles<br>-stand<br>Introd<br>IEEE<br>6.2.1<br>6.2.2                                                              | lardized operation on IEEE Std 802.11 hardware         uction         Std 802.11         Distributed Coordination Function (DCF)         Quality of Service | <ol> <li>191</li> <li>191</li> <li>193</li> <li>194</li> <li>197</li> </ol>                                                                  |

|         | <b>W</b><br><b>Non</b><br>6.1        | 7 <b>ireles</b><br>- <b>stand</b><br>Introd<br>IEEE<br>6.2.1<br>6.2.2<br>6.2.3                                     | lardized operation on IEEE Std 802.11 hardware         uction                                                                                               | <ol> <li>191</li> <li>193</li> <li>194</li> <li>197</li> <li>198</li> </ol>                                                                  |

|         | <b>W</b><br><b>Non</b><br>6.1        | 7 <b>ireles</b><br>- <b>stand</b><br>Introd<br>IEEE<br>6.2.1<br>6.2.2<br>6.2.3<br>6.2.4<br>6.2.5                   | lardized operation on IEEE Std 802.11 hardware         uction                                                                                               | <ol> <li>191</li> <li>193</li> <li>194</li> <li>197</li> <li>198</li> <li>199</li> </ol>                                                     |

|         | <b>W</b><br><b>Non</b><br>6.1<br>6.2 | 7 <b>ireles</b><br>- <b>stand</b><br>Introd<br>IEEE<br>6.2.1<br>6.2.2<br>6.2.3<br>6.2.4<br>6.2.5                   | lardized operation on IEEE Std 802.11 hardware         uction                                                                                               | <ol> <li>191</li> <li>191</li> <li>193</li> <li>194</li> <li>197</li> <li>198</li> <li>199</li> <li>200</li> </ol>                           |

|         | <b>W</b><br><b>Non</b><br>6.1<br>6.2 | 7 <b>ireles</b><br>- <b>stand</b><br>Introd<br>IEEE<br>6.2.1<br>6.2.2<br>6.2.3<br>6.2.4<br>6.2.5<br>Relate         | ardized operation on IEEE Std 802.11 hardware         uction                                                                                                | <ol> <li>191</li> <li>191</li> <li>193</li> <li>194</li> <li>197</li> <li>198</li> <li>199</li> <li>200</li> <li>201</li> </ol>              |

|         | <b>W</b><br><b>Non</b><br>6.1<br>6.2 | 7 <b>ireles</b><br><b>-stand</b><br>Introd<br>IEEE<br>6.2.1<br>6.2.2<br>6.2.3<br>6.2.4<br>6.2.5<br>Relate<br>6.3.1 | ardized operation on IEEE Std 802.11 hardware         uction                                                                                                | <ol> <li>191</li> <li>191</li> <li>193</li> <li>194</li> <li>197</li> <li>198</li> <li>199</li> <li>200</li> <li>201</li> <li>201</li> </ol> |

|   |     | 6.3.4  | Power Efficiency                                                                           | 207 |

|---|-----|--------|--------------------------------------------------------------------------------------------|-----|

|   |     | 6.3.5  | Kernel performance analysis                                                                | 208 |

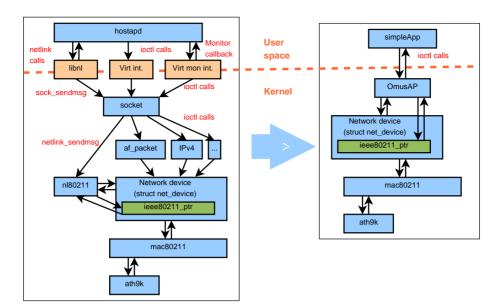

|   | 6.4 | Linux  | kernel                                                                                     | 209 |

|   |     | 6.4.1  | Process management                                                                         | 209 |

|   |     | 6.4.2  | Interrupt handling $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 213 |

|   |     | 6.4.3  | Timers                                                                                     | 214 |

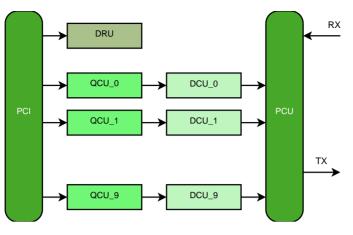

|   |     | 6.4.4  | Networking architecture                                                                    | 217 |

|   | 6.5 | Real-T | Time Systems                                                                               | 224 |

|   | 6.6 | Conclu | ision                                                                                      | 228 |

| 7 | Tra | nsmiss | ion control on a IEEE Std 802.11n compliant NIC                                            | 231 |

|   | 7.1 | Introd | uction                                                                                     | 231 |

|   | 7.2 | Timer  | source analysis                                                                            | 233 |

|   |     | 7.2.1  | Timer source identification                                                                | 234 |

|   |     | 7.2.2  | Real-Time Operating Systems                                                                | 237 |

|   |     | 7.2.3  | Timer analysis methodology                                                                 | 237 |

|   | 7.3 | Timer  | analysis results                                                                           | 239 |

|   |     | 7.3.1  | The hrtimer performance                                                                    | 239 |

|   |     | 7.3.2  | The hrtimer in different kernels and the SWBA timer $\ . \ . \ .$                          | 241 |

|   |     | 7.3.3  | The hrtimer performance and dynticks or network transfers .                                | 243 |

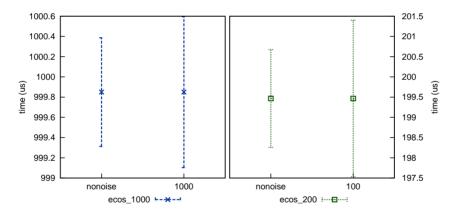

|   |     | 7.3.4  | Proprietary real-time timer analysis                                                       | 245 |

|   |     | 7.3.5  | Real-time Operating System timers                                                          | 247 |

|   |     | 7.3.6  | Conclusion                                                                                 | 250 |

|   | 7.4 | Reliab | le TX on IEEE Std 802.11n hardware                                                         | 251 |

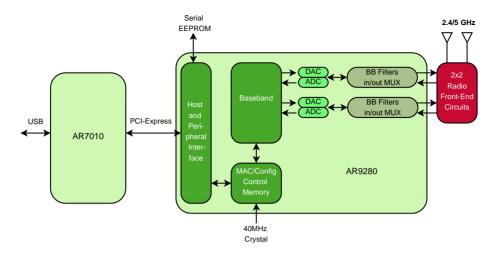

|   |     | 7.4.1  | System description                                                                         | 251 |

|   |     | 7.4.2  | Common issues and misconceptions                                                           | 255 |

|   |     | 7.4.3  | Hardware controlled operation                                                              | 256 |

|   |     | 7.4.4  | Software controlled operation                                                              | 257 |

| 7.5 | Imple | mentation of controlled transmissions $\ldots \ldots \ldots \ldots \ldots 258$                         |

|-----|-------|--------------------------------------------------------------------------------------------------------|

|     | 7.5.1 | hostapd                                                                                                |

|     | 7.5.2 | ath9k 260                                                                                              |

|     | 7.5.3 | Reliable TX Performance Results                                                                        |

| 7.6 | Concl | usion $\ldots \ldots 265$ |

269

### III Cognitive Radio Networks

| 8                                            | Ren      | idezvo                              | us in Cognitive Radio Networks              | 271 |

|----------------------------------------------|----------|-------------------------------------|---------------------------------------------|-----|

|                                              | 8.1      | Introd                              | $\operatorname{luction}$                    | 271 |

|                                              | 8.2      | Chanr                               | nel Hopping based Rendezvous                | 273 |

|                                              | 8.3      | Defini                              | tions                                       | 274 |

|                                              |          | 8.3.1                               | Quorum Systems                              | 274 |

|                                              |          | 8.3.2                               | Cyclic Difference Set                       | 276 |

|                                              |          | 8.3.3                               | Latin Square                                | 277 |

|                                              |          | 8.3.4                               | Identical Row Square                        | 277 |

| 8.4 Related Neighborhood Discovery Protocols |          | ed Neighborhood Discovery Protocols | 277                                         |     |

|                                              |          | 8.4.1                               | Random based Rendezvous                     | 278 |

|                                              |          | 8.4.2                               | Number Theory based Rendezvous              | 280 |

|                                              |          | 8.4.3                               | Logic Contemplation based Rendezvous        | 282 |

|                                              |          | 8.4.4                               | Guarantee System based Rendezvous           | 283 |

|                                              | 8.5      | Concl                               | usion                                       | 285 |

| 9                                            | <b>A</b> | mahnar                              | nous operation in Cognitive Radio Networks  | 287 |

| 9                                            | Asy      | nenroi                              | nous operation in Cognitive Radio Networks  | 201 |

|                                              | 9.1      | Introd                              | luction                                     | 287 |

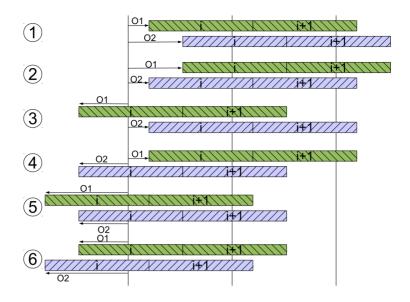

|                                              | 9.2      | Symm                                | etric Asynchronous RDV Analysis             | 289 |

|                                              |          | 9.2.1                               | Mirror Torus-in-Grid quorum system (mT-Gqs) | 290 |

|                                              |          | 9.2.2                               | Asynchronous analysis                       | 291 |

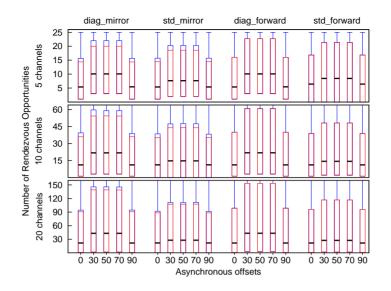

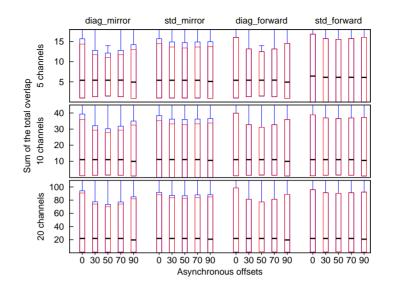

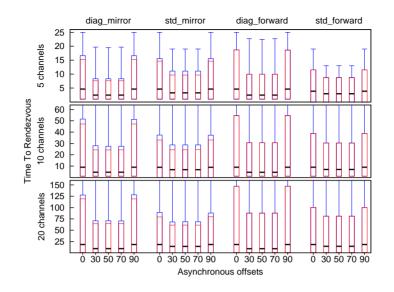

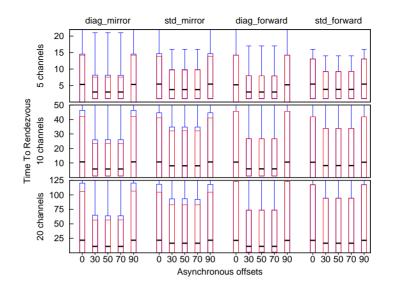

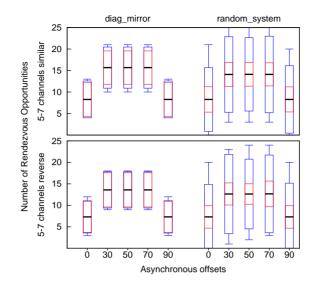

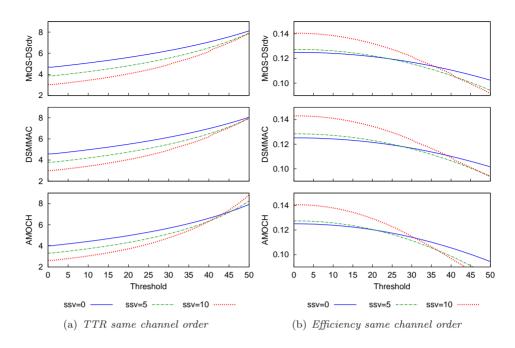

|     | 9.2.3 | Performance evaluation                          |

|-----|-------|-------------------------------------------------|

| 9.3 | Asym  | metric Asynchronous RDV Analysis                |

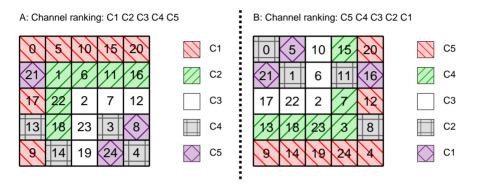

|     | 9.3.1 | Asynchronous Rendezvous Extension               |

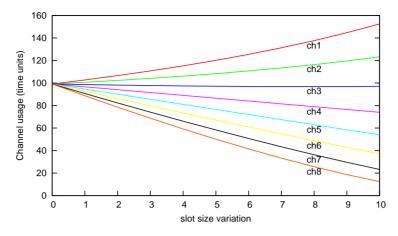

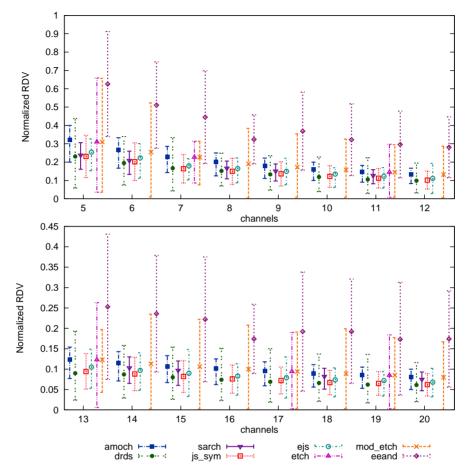

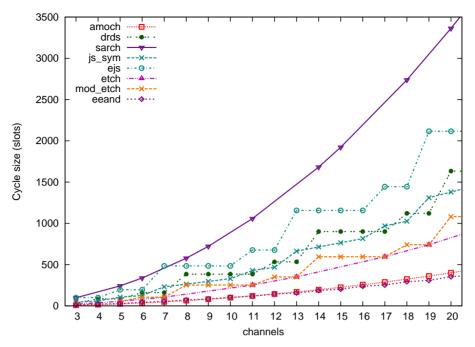

|     | 9.3.2 | Performance evaluation                          |

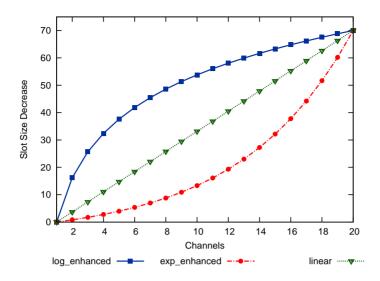

| 9.4 | Enhar | nced Asynchronous Rendezvous Extensions         |

|     | 9.4.1 | EAND hopping sequence                           |

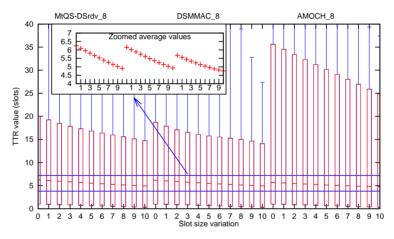

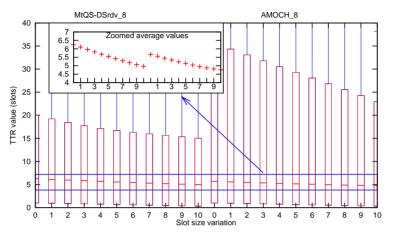

|     | 9.4.2 | Enhanced Asynchronous Rendezvous Extensions 313 |

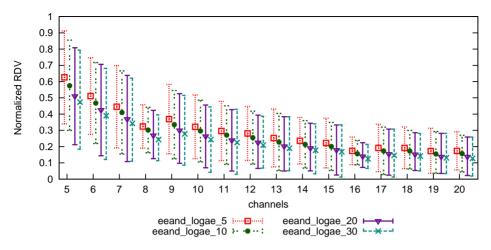

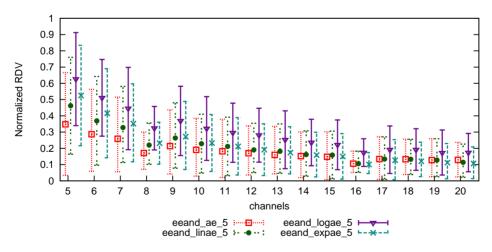

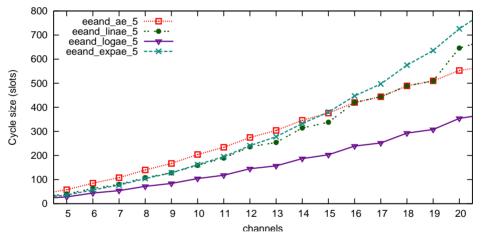

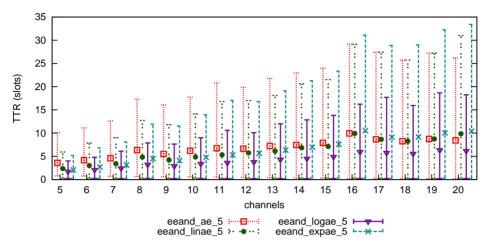

|     | 9.4.3 | Performance Evaluation                          |

| 9.5 | Concl | usion                                           |

|     |       |                                                 |

#### 10 Conclusion and Perspectives

References

## List of Tables

| 7.1 | Deviations larger than 1 $\mu s$ for the first test $\hdots \hdots \hdots$ | 264 |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 7.2 | Deviations larger than 1 $\mu s$ for the second test $\hdots \ldots \ldots \ldots \ldots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 265 |

| 9.1 | asynchronous evaluation in a heterogeneous network                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 298 |

# List of Figures

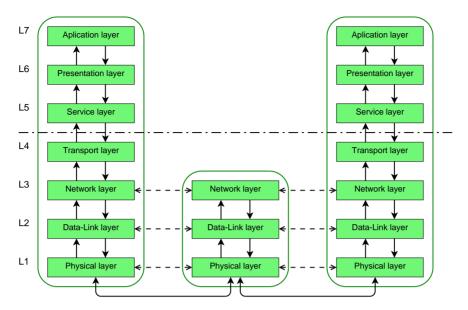

| 1.1  | ISO OSI reference model                                                          | 5  |

|------|----------------------------------------------------------------------------------|----|

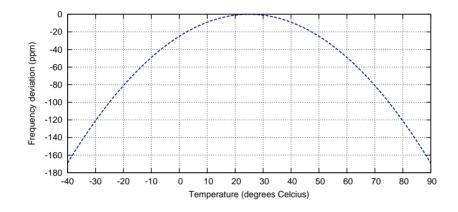

| 4.1  | Typical Crystal Frequency deviation due to temperature                           | 66 |

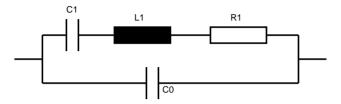

| 4.2  | Equivalent electrical circuit of a crystal                                       | 67 |

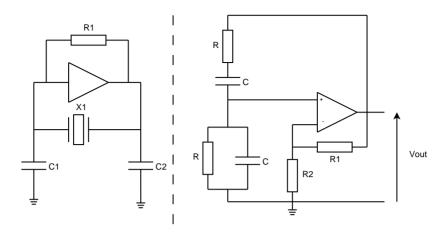

| 4.3  | Pierce oscillator (left) and RC oscillator (right) $\ldots \ldots \ldots \ldots$ | 68 |

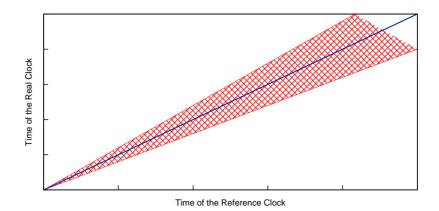

| 4.4  | Time drift of a clock                                                            | 70 |

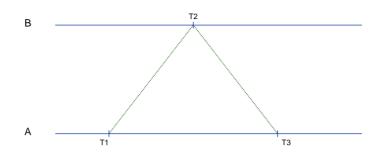

| 4.5  | Cristians algorithm, message flow and timing                                     | 72 |

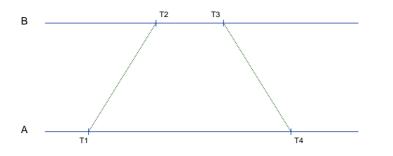

| 4.6  | NTP, message flow and timing                                                     | 73 |

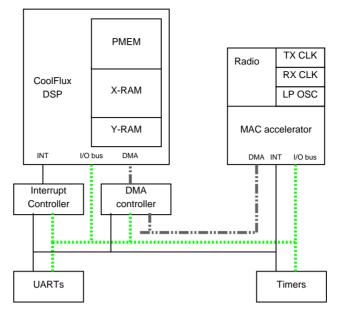

| 4.7  | Simplified block diagram of Magnetic Induction Radio IC $\ldots$ .               | 82 |

| 4.8  | MIRA Transmission and Reception timing                                           | 83 |

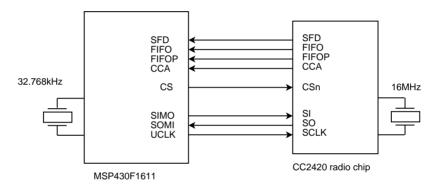

| 4.9  | Simplified block diagram of TelosB sensor platform                               | 84 |

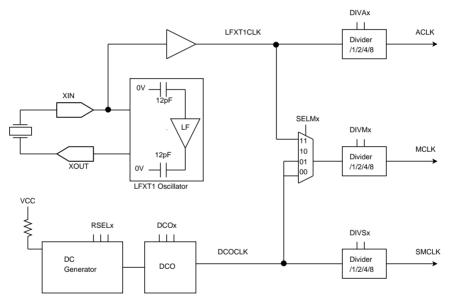

| 4.10 | Simplified clock diagram of MSP430F1611                                          | 85 |

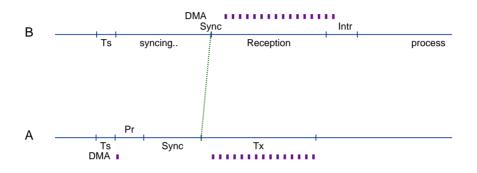

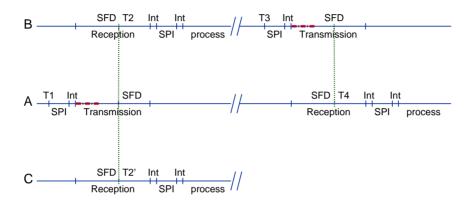

| 4.11 | TelosB Transmission and Reception timing                                         | 87 |

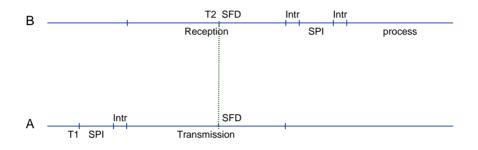

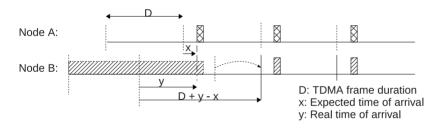

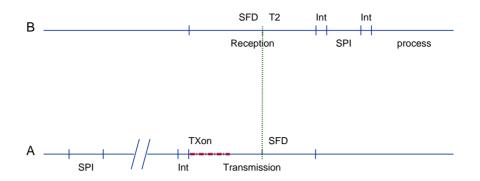

| 4.12 | 2-way message exchange on hardware                                               | 89 |

| 4.13 | Synchronization process                                                          | 93 |

| 4.14 | Slot based synchronization on hardware                                           | 96 |

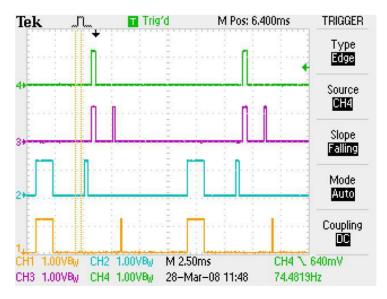

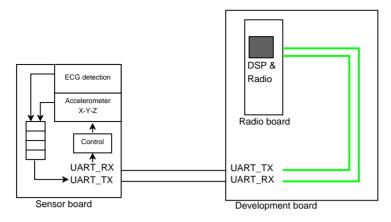

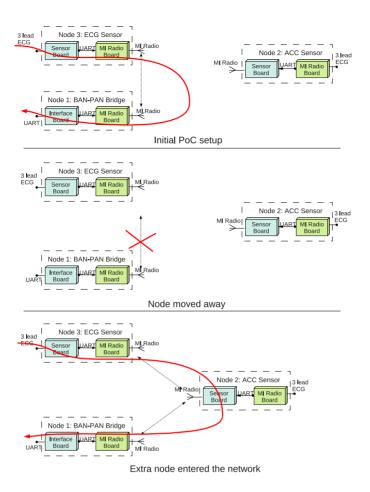

| 4.15 | PoC setup                                                                        | 97 |

| 4.16 PoC scope communication detail                                                                                     | 98  |

|-------------------------------------------------------------------------------------------------------------------------|-----|

| $4.17$ Simplified block diagram of Magnetic Induction Radio IC platform $% 10^{-1}$ .                                   | 100 |

| 4.18 PoC setup: extra node entered                                                                                      | 101 |

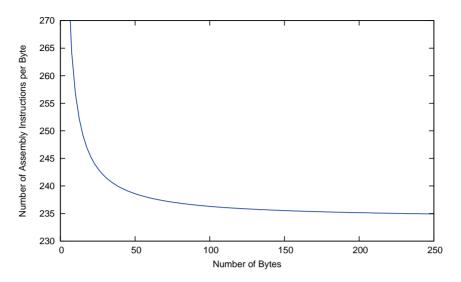

| 5.1 Required number of instructions to account for raw data transmission                                                | 111 |

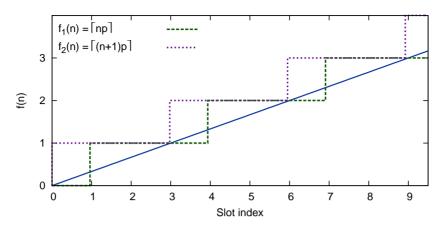

| 5.2 $f_1$ and $f_2$ of MRBS with asymptotic mean equal to $1/3$                                                         | 119 |

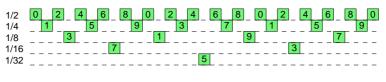

| 5.3 Slot allocation for $\frac{1}{2} + \frac{1}{4} + \frac{1}{8} + \frac{1}{16} + \frac{1}{32} + \dots + \dots + \dots$ | 129 |

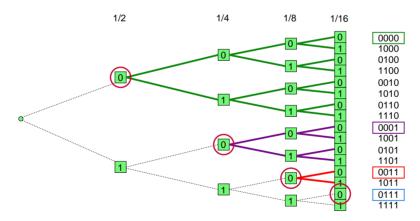

| 5.4 Binary search tree                                                                                                  | 129 |

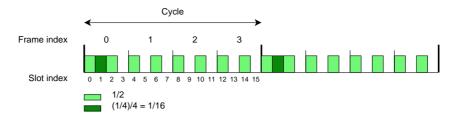

| 5.5 Allocation of 9/16 in a 4 slot period $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$                     | 136 |

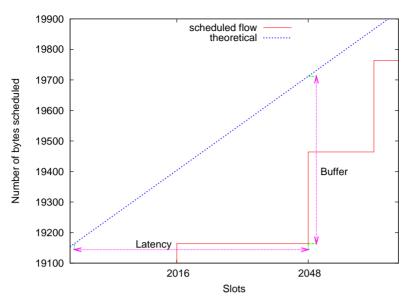

| 5.6 Latency and Buffer size definitions                                                                                 | 139 |

| 5.7 Transmission pattern of 77 Bps with 300B slots $(\frac{1}{4} + \frac{1}{128})$                                      | 140 |

| 5.8 Buffer size of 77 Bps with 300B slots $(\frac{1}{4} + \frac{1}{128})$                                               | 141 |

| 5.9 Buffer size of 79 Bps with 300B slots $(\frac{1}{4} + \frac{1}{64})$                                                | 142 |

| 5.10 Latency of 77 Bps with 300B slots $(\frac{1}{4} + \frac{1}{128}) \dots \dots \dots \dots$                          | 143 |

| 5.11 Transmission pattern of 95Bps with 300B slots $(\frac{1}{4} + \frac{1}{16} + \frac{1}{128})$                       | 144 |

| 5.12 Buffer size of 95Bps with 300B slots $\left(\frac{1}{4} + \frac{1}{16} + \frac{1}{128}\right)$                     | 145 |

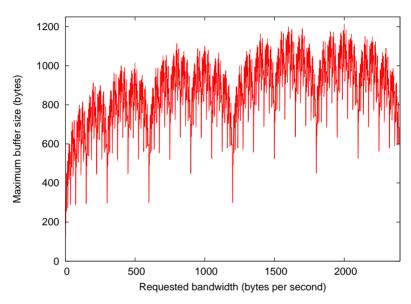

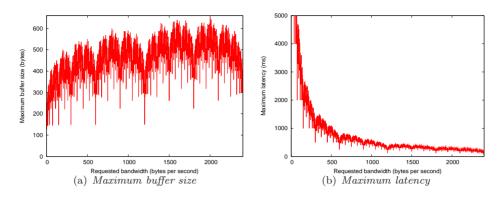

| 5.13 Max buffer size vs bandwidth request for 300B slots $\ldots \ldots \ldots$                                         | 146 |

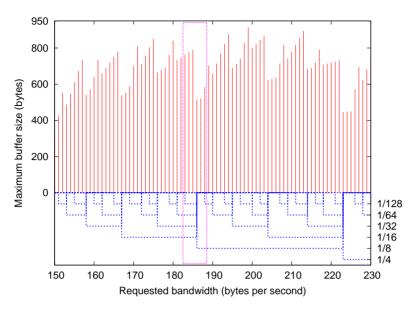

| 5.14 Section of max buffer size vs bandwidth request for 300B slots $\ .$ .                                             | 147 |

| 5.15 Latency of 95Bps with 300B slots $(\frac{1}{4} + \frac{1}{16} + \frac{1}{128})$                                    | 155 |

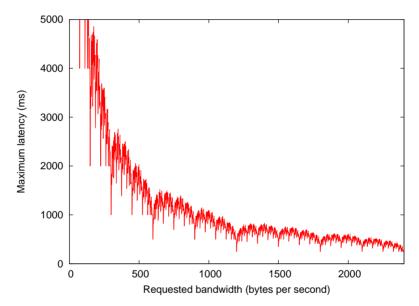

| 5.16 Max latency vs bandwidth request for 300B slots $\ldots \ldots \ldots \ldots$                                      | 156 |

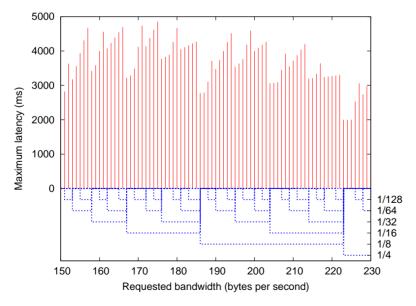

| 5.17 Section of max latency vs bandwidth request for 300B slots $\ . \ . \ .$                                           | 157 |

| 5.18 Maxima with denominator limited to $\frac{1}{16}$                                                                  | 159 |

| 5.19 Maxima vs bandwidth request for 150B slots $\ldots \ldots \ldots \ldots \ldots$                                    | 160 |

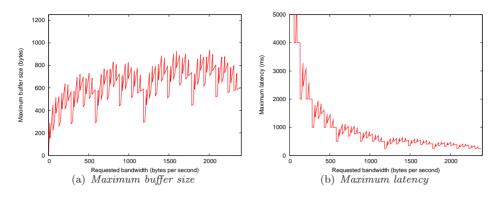

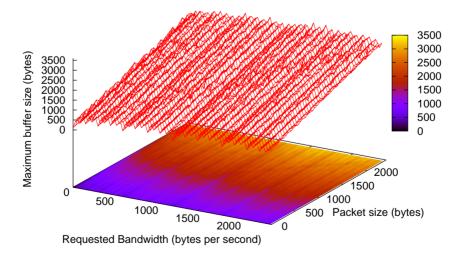

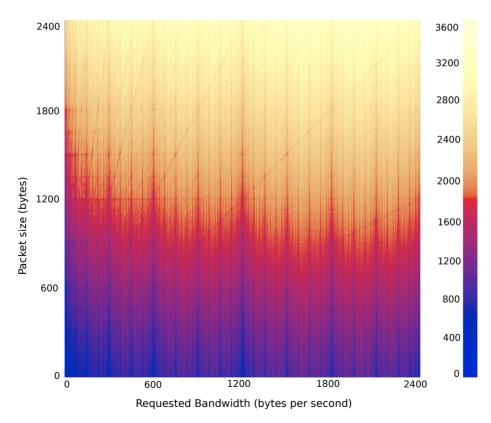

| 5.20 Maximum buffer size vs the requested bandwidth and the packet size                                                 | 161 |

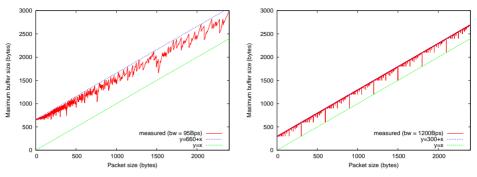

| 5.21 Maximum buffer size for each rate versus the packet size                                                           | 163 |

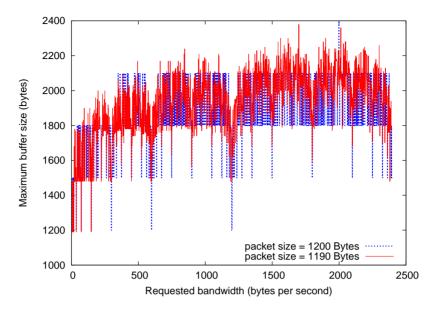

| 5.22 Max buffer size vs the bandwidth, bursts of 1190B and 1200B                                                        | 164 |

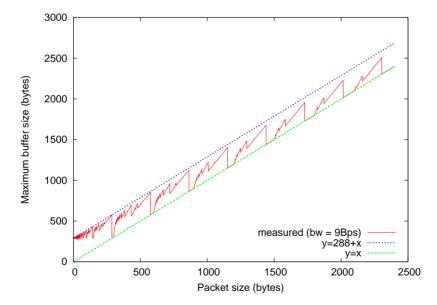

| 5.23 Max buffer size versus the packet size, 9Bps bandwidth request                                                     | 164 |

| 5.24 Maximum buffer size versus the packet size                                                                         | 166 |

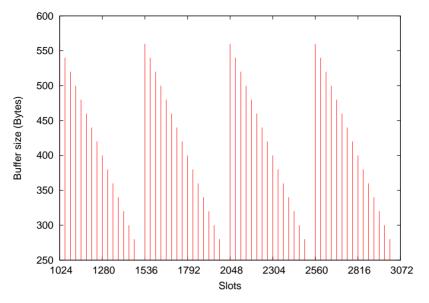

| 5.25 | Buffer size of 70Bps with 300B slots and bursts of 280B $\ .$                                                            | 167 |

|------|--------------------------------------------------------------------------------------------------------------------------|-----|

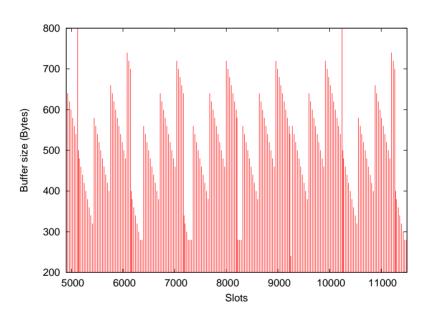

| 5.26 | Buffer size of 77Bps with 300B slots and bursts of 280B $\ .$                                                            | 168 |

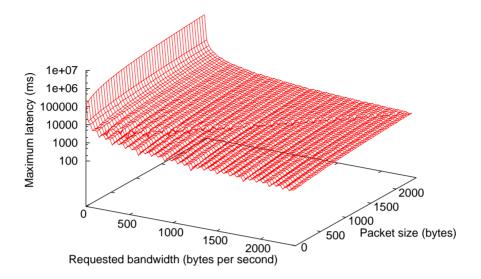

| 5.27 | Maximum latency vs the requested bandwidth and the packet size $% \left( {{{\bf{x}}_{i}}} \right)$ .                     | 170 |

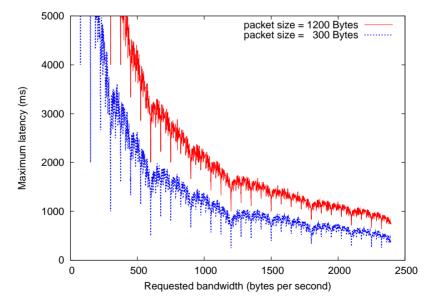

| 5.28 | Max latency vs the requested bandwidth, bursts of 300B and 1200B $$                                                      | 170 |

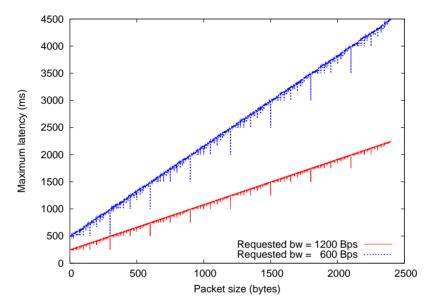

| 5.29 | Maximum latency vs the packet size, 600Bps and 1200Bps bandwidth                                                         | 171 |

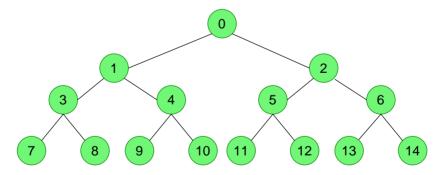

| 5.30 | The network topology and node numbering                                                                                  | 172 |

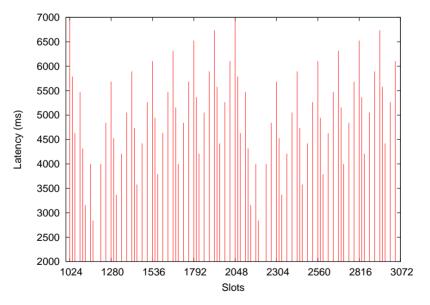

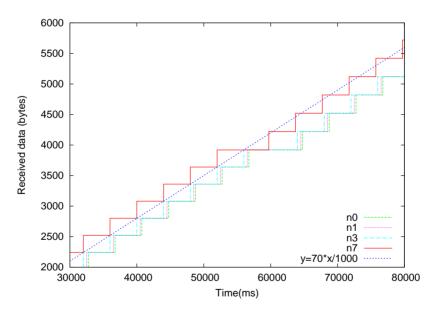

| 5.31 | Received data originating from node 7 at a rate of 70Bps $\ldots$ .                                                      | 173 |

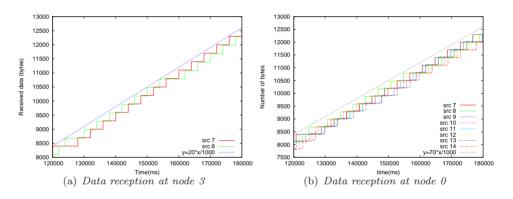

| 5.32 | The received data from the perspective of nodes 3 and 0                                                                  | 174 |

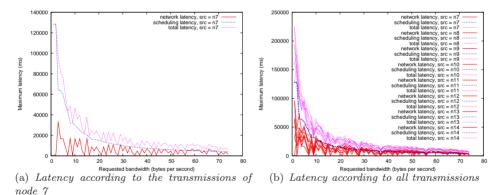

| 5.33 | Maximum latency vs the bandwidth request                                                                                 | 175 |

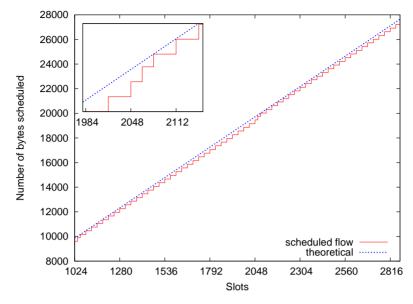

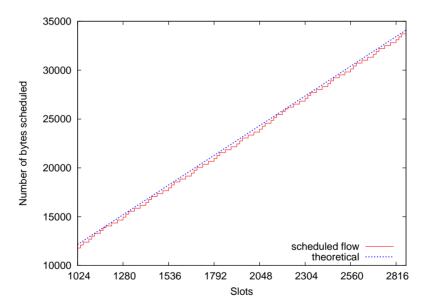

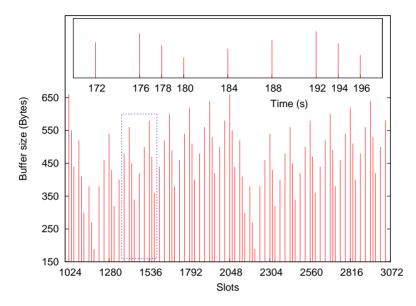

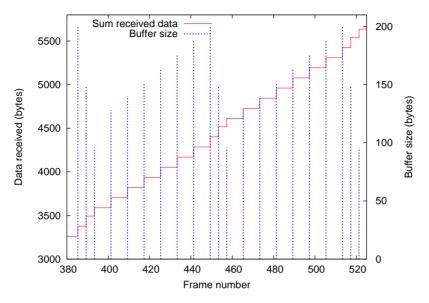

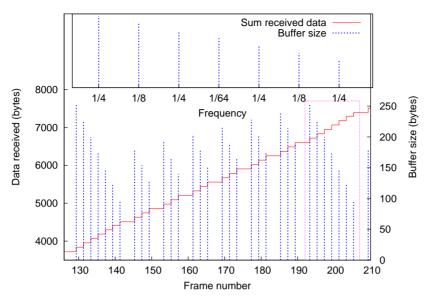

| 5.34 | Data arrival and buffer size at a bandwidth of 16 bytes per frame                                                        | 181 |

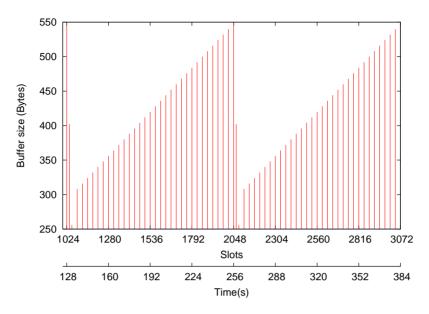

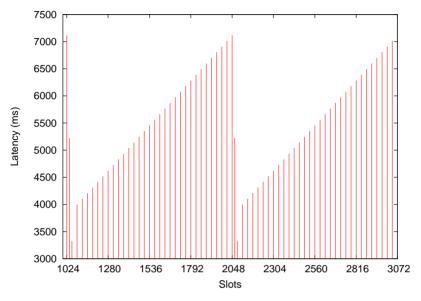

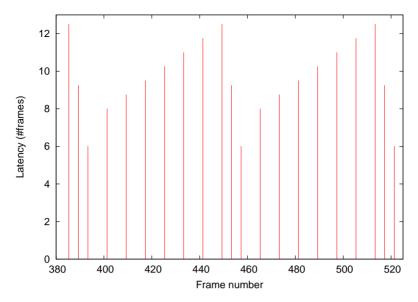

| 5.35 | Latency at a bandwidth of 16 bytes per frame                                                                             | 182 |

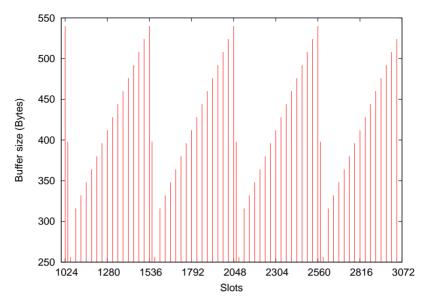

| 5.36 | Data arrival and buffer size at a bandwidth of 45 bytes per frame                                                        | 183 |

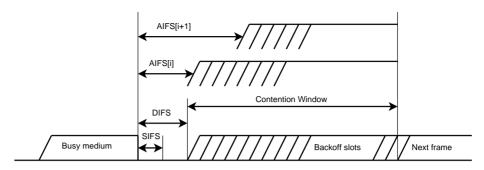

| 6.1  | IEEE Std 802.11-2012 Interframe space                                                                                    | 194 |

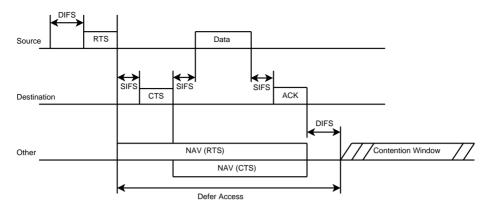

| 6.2  | IEEE Std 802.11 RTS/CTS/data procedure                                                                                   | 196 |

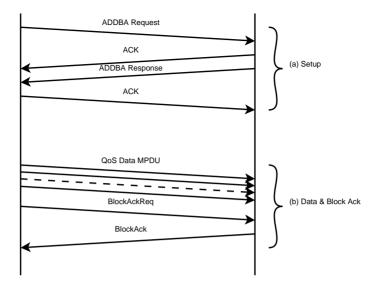

| 6.3  | IEEE Std 802.11 Block Ack mechanism                                                                                      | 198 |

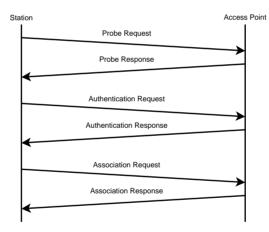

| 6.4  | IEEE Std 802.11 Infrastructure BSS association procedure                                                                 | 200 |

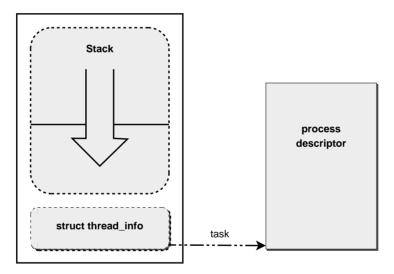

| 6.5  | Allocated kernel memory for a process                                                                                    | 210 |

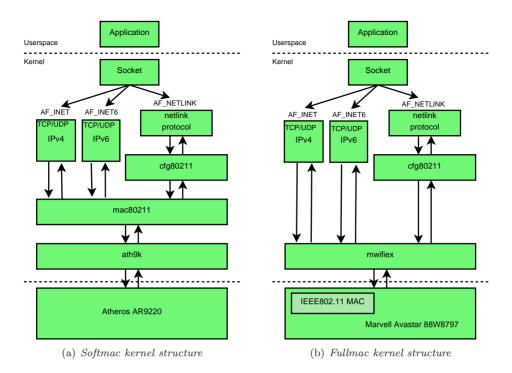

| 6.6  | SoftMAC and fullMAC concepts                                                                                             | 220 |

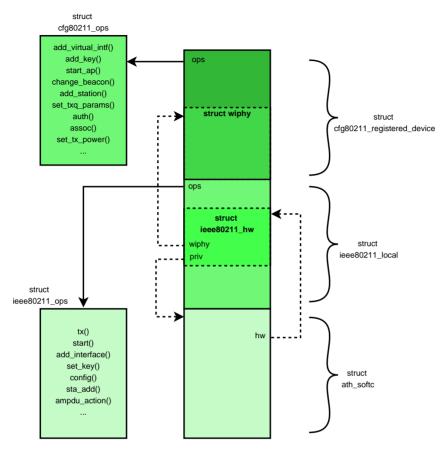

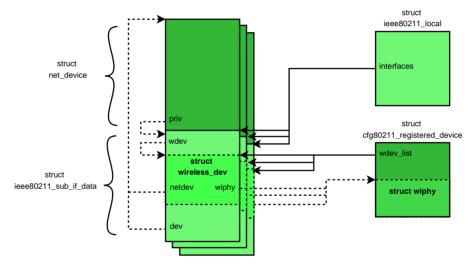

| 6.7  | Physical interface representation                                                                                        | 221 |

| 6.8  | Virtual interface representation                                                                                         | 222 |

|      |                                                                                                                          |     |

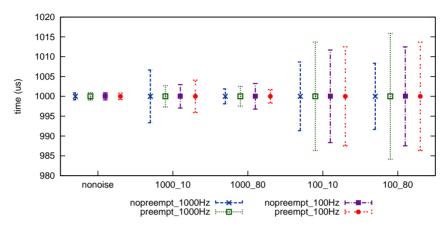

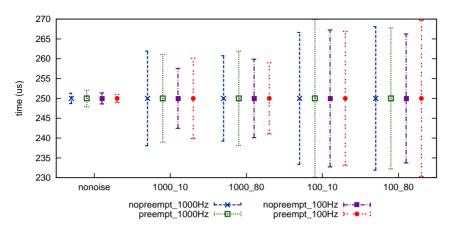

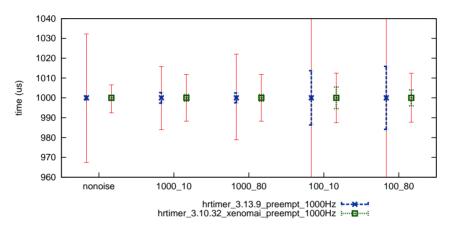

| 7.1  | 3.13.9 hr<br>timer, variation of preemption and HZ, 1000 $\upmu$ interval<br>~                                           | 240 |

| 7.2  | 3.13.9 hr<br>timer, variation of preemption and HZ, 250 $\upmu$ interval<br>$\ .$                                        | 241 |

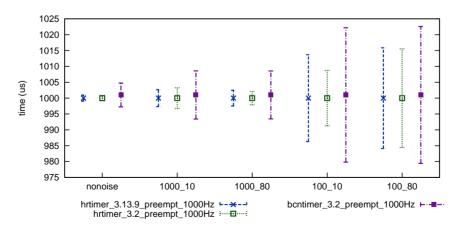

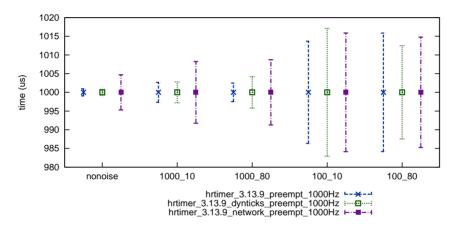

| 7.3  | SWBA timer vs 3.2 and 3.13.9 hrtimer, 1000 $\mu s$ interval $\ldots$ .                                                   | 241 |

| 7.4  | SWBA timer vs 3.2 and 3.13.9 hrtimer, 250 µs interval                                                                    | 242 |

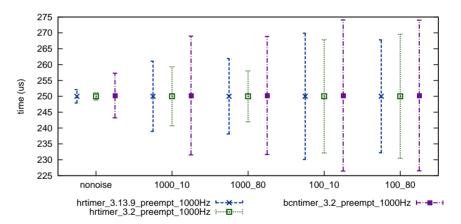

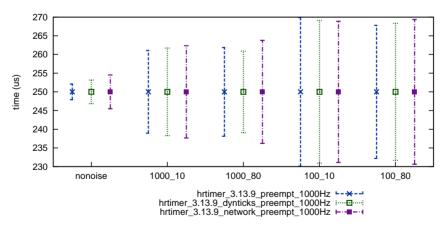

| 7.5  | 3.13.9 hr<br>timer vs dynticks and network operation, 1000 $\ensuremath{\mu s}$<br>interval $% \ensuremath{\lambda s}$ . | 243 |

| 7.6  | 3.13.9 hr<br>timer vs dynticks and network operation, 250 $\upmu$ interval<br>                                           | 243 |

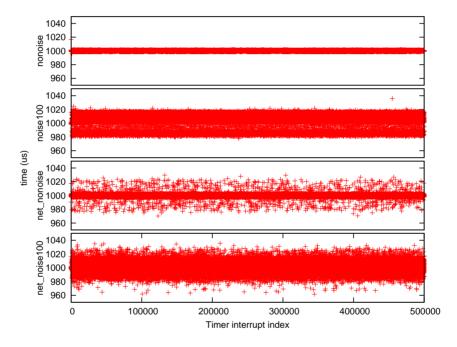

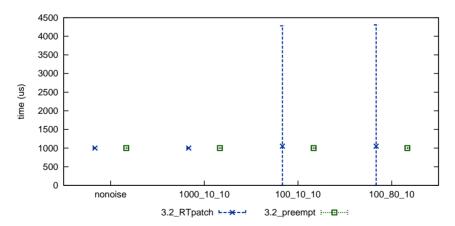

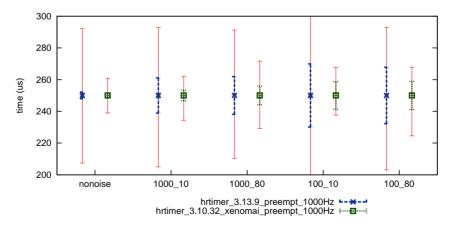

| 7.7  | inter-arrival time 3.13.9 hr<br>timer and network load, 1000 $\ensuremath{\mu s}$ interval .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 244 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

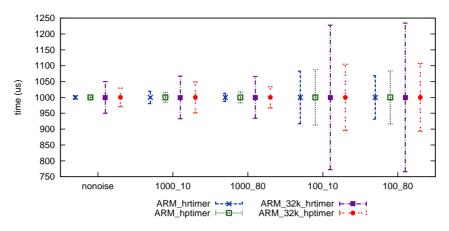

| 7.8  | Hrtimer and hptimer on ARM-Cortex A8, 1000 µs interval                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 246 |

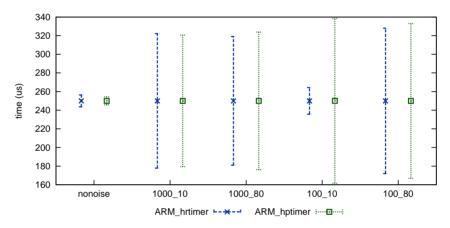

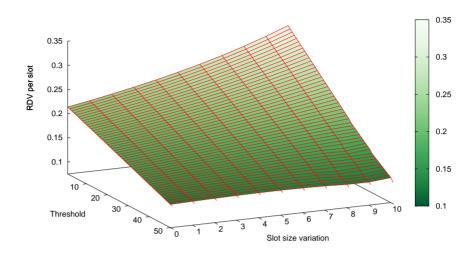

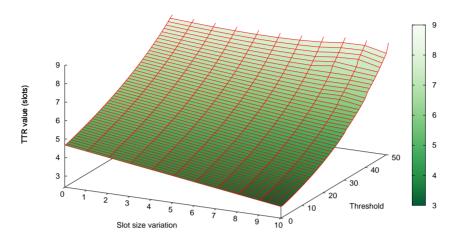

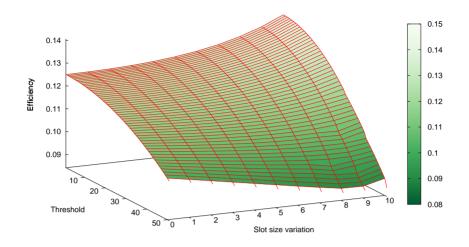

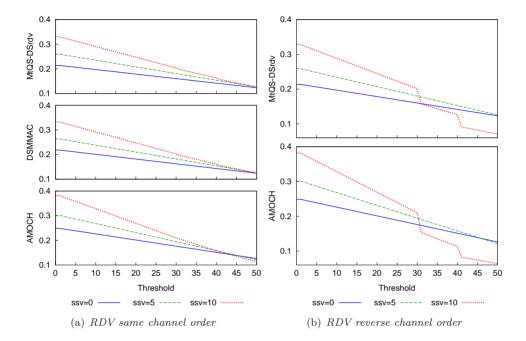

| 7.9  | Hr<br>timer and hptimer on ARM-Cortex A8, 250 $\mu s$ interval<br>$\ .$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 246 |